- 您现在的位置:买卖IC网 > Sheet目录311 > AS5140 PB (ams)BOARD PROGRAM AS5140

�� �

�

�

�AS5140H�

�Data� Sheet� -� D� e� t� a� i� l� e� d� D� e� s� c� r� i� p� t� i� o� n�

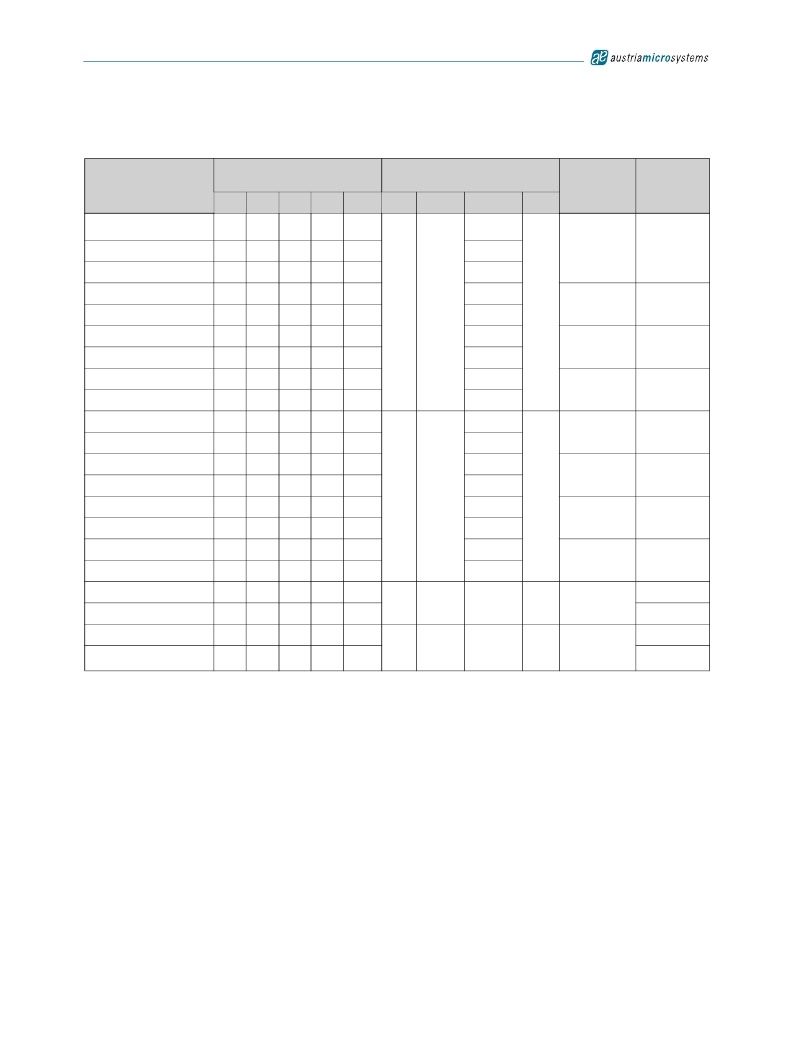

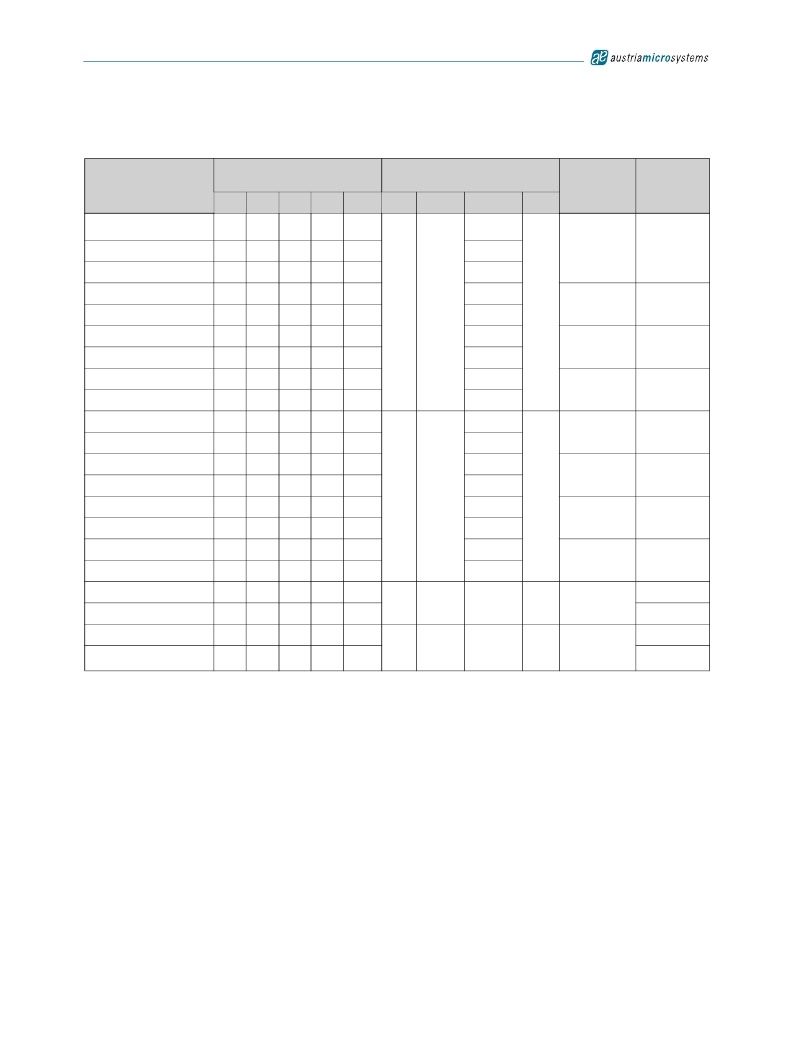

�Table� 20.� One� Time� Programmable� (OTP)� Register� Options�

�Mode�

�OTP-Mode-Register-Bit�

�Pin#�

�Pulses� per�

�Revolution�

�Incremental�

�Resolution�

�Default� (Mode0.0)�

�quadAB-Mode1.0�

�1�

�Md1�

�0�

�0�

�Md0�

�0�

�1�

�Div1� Div0�

�0�

�0�

�0�

�0�

�Index�

�0�

�0�

�3�

�4�

�6�

�1LSB�

�1LSB�

�12�

�ppr�

�2� x� 256�

�bit�

�10�

�quadAB-Mode1.1�

�0�

�1�

�0�

�0�

�1�

�3LSBs�

�quadAB-Mode1.2�

�quadAB-Mode1.3�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�A�

�B�

�1LSB�

�3LSBs�

�PWM�

�10� bit�

�2� x� 128�

�9�

�quadAB-Mode1.4�

�quadAB-Mode1.5�

�quadAB-Mode1.6�

�quadAB-Mode1.7�

�Step/Dir-Mode2.0�

�Step/Dir-Mode2.1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�0�

�0�

�0�

�1�

�0�

�1�

�0�

�1�

�1LSB�

�3LSBs�

�1LSB�

�3LSBs�

�1LSB�

�3LSBs�

�2� x� 64�

�2� x� 32�

�512�

�8�

�7�

�10�

�Step/Dir� -Mode2.2�

�Step/Dir� -Mode2.3�

�Step/Dir� -Mode2.4�

�Step/Dir� -Mode2.5�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�0�

�1�

�LSB�

�Dir�

�1LSB�

�3LSBs�

�1LSB�

�3LSBs�

�PWM�

�10� bit�

�256�

�128�

�9�

�8�

�Step/Dir� -Mode2.6�

�Step/Dir� -Mode2.7�

�1�

�1�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�1�

�1LSB�

�3LSBs�

�64�

�7�

�Commutation-Mode3.0�

�Commutation-Mode3.1�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�0�

�0�

�U(0o)�

�V(120o)�

�W(240o)�

�LSB�

�3� x� 1�

�10�

�9�

�W’�

�(0o,18� (60o,240o� (120o,300o)�

�Commutation-Mode3.2�

�Commutation-Mode3.3�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�1�

�0�

�0�

�U’� V’�

�0o)� )�

�LSB�

�2� x� 3�

�10�

�9�

�1.� Div1,� Div0� and� Index� cannot� be� programmed� in� Mode� 0:0�

�7.6.7�

�Zero� Position� Programming�

�Zero� position� programming� is� an� OTP� option� that� simplifies� assembly� of� a� system,� as� the� magnet� does� not� need� to� be� manually� adjusted� to� the�

�mechanical� zero� position.� Once� the� assembly� is� completed,� the� mechanical� and� electrical� zero� positions� can� be� matched� by� software.� Any�

�position� within� a� full� turn� can� be� defined� as� the� permanent� new� zero/index� position.� For� zero� position� programming,� the� magnet� is� turned� to� the�

�mechanical� zero� position� (e.g.� the� “off”-position� of� a� rotary� switch)� and� the� actual� angular� value� is� read.�

�7.7� Alignment� Mode�

�The� alignment� mode� simplifies� centering� the� magnet� over� the� center� of� the� chip� to� gain� maximum� accuracy.� Alignment� mode� can� be� enabled� with�

�the� falling� edge� of� CSn� while� Prog� =� logic� high� (see� Figure� 16)� .� The� Data� bits� D9-D0� of� the� SSI� change� to� a� 10-bit� displacement� amplitude�

�output.� A� high� value� indicates� large� X� or� Y� displacement,� but� also� higher� absolute� magnetic� field� strength.� The� magnet� is� properly� aligned,� when�

�the� difference� between� highest� and� lowest� value� over� one� full� turn� is� at� a� minimum.� Under� normal� conditions,� a� properly� aligned� magnet� will�

�result� in� a� reading� of� less� than� 128� over� a� full� turn.� The� MagINCn� and� MagDECn� indicators� will� be� =� 1� when� the� alignment� mode� reading� is� <� 128.�

�At� the� same� time,� both� hardware� pins� MagINCn� (#1)� and� MagDECn� (#2)� will� be� pulled� to� VSS.� A� properly� aligned� magnet� will� therefore� produce�

�a� MagINCn� =� MagDECn� =� 1� signal� throughout� a� full� 360o� turn� of� the� magnet.� Stronger� magnets� or� short� gaps� between� magnet� and� IC� may� show�

�values� larger� than� 128.� These� magnets� are� still� properly� aligned� as� long� as� the� difference� between� highest� and� lowest� value� over� one� full� turn� is�

�at� a� minimum.� The� Alignment� mode� can� be� reset� to� normal� operation� by� a� power-on-reset� (disconnect� /� re-connect� power� supply)� or� by� a� falling�

�edge� on� CSn� with� Prog� =� low.�

�www.austriamicrosystems.com/AS5140H�

�Revision� 1.4�

�22� -� 37�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ASDMB-ADAPTER-KIT

ASDMB MEMSPEED P II OSC KIT

ASFLMPLP-ADAPTER-KIT

ASFLMPLP MEMSPEED P II OSC KIT

AT24C01-10SI-1.8

IC EEPROM 1KBIT 400KHZ 8SOIC

AT24C01B-TSU-T

IC EEPROM 1KBIT 1MHZ SOT23-5

AT24C02C-XHM-B

IC EEPROM 2KBIT 1MHZ 8TSSOP

AT24C04AN-10SI-2.7

IC EEPROM 4KBIT 400KHZ 8SOIC

AT24C08B-PU

IC EEPROM 8KBIT 1MHZ 8DIP

AT24C1024B-TH25-B

IC EEPROM 1MBIT 1MHZ 8TSSOP

相关代理商/技术参数

AS51400FLF

制造商:TT Electronics / IRC 功能描述:AS51400FLF

AS51400HLF

制造商:TT Electronics / IRC 功能描述:AS51400HLF

AS51400JLF

制造商:TT Electronics / IRC 功能描述:AS51400JLF

AS51401FLF

制造商:TT Electronics / IRC 功能描述:AS51401FLF

AS51401HLF

制造商:TT Electronics / IRC 功能描述:AS51401HLF

AS51401JLF

制造商:TT Electronics / IRC 功能描述:AS51401JLF

AS51402FLF

制造商:TT Electronics / IRC 功能描述:AS51402FLF

AS51402HLF

制造商:TT Electronics / IRC 功能描述:AS51402HLF